### **TOSHIBA**

INTEGRATED CIRCUIT TECHNICAL DATA

## **MICROCOMPUTER**

# LSI DATA BOOK

**July 1984**

**TOSHIBA CORPORATION**

TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT

TMP8049P/8049P-6/8049PI-6

TMP8039P/8039P-6/8039PI-6

N-CHANNEL SILICON GATE MOS

8-BIT SINGLE-CHIP MICROCOMPUTER

#### GENERAL DESCRIPTION

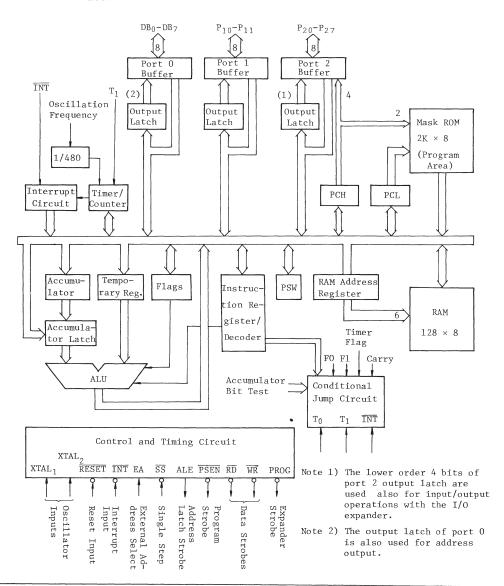

The TMP8049P, from here on referred to as the TMP8049, is a single chip microcomputer fabricated in N-channel Silicon Gate MOS technology which provides internal 8-bit parallel architecture.

The following basic architectural functions of a computer have been included in a single chip; an 8-bit CPU,  $128\times8$  RAM data memory,  $2K\times8$  ROM program memory, 27 I/O lines and an 8-bit timer/event counter.

The TMP8049 is particularly efficient as a controller. It has extensive bit handling capability as well as facilities for both binary and BCD arithmetic.

The TMP8039P is the equivalent of a  $\cdot$ TMP8049 without ROM program memory on chip. By using this device with external EPROM or RAM, software debugging becomes easy.

The TMP8049P-6/TMP8039P-6 is a lower speed (6MHz) version of the TMP8049P/TMP8039P.

#### **FEATURES**

- · Compatible with Intel's 8049

- 1.36µS Instruction Cycle

- · All instruction 1 or 2 cycles

- · Over 90 instructions; 70% single byte

- Easy expandable memory and I/O

- 2K × 8 masked ROM

- 128 × 8 RAM

- · 27 I/O lines

- · Interval Timer/Event Counter

- · Single level interrupt

- · Single 5V supply

- -40°C to +85°C Operation (TMP8049PI-6/ TMP8039PI-6: Industrial Specification)

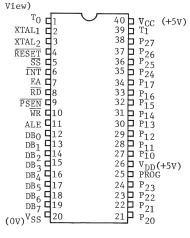

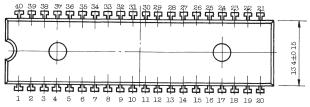

#### PIN CONNECTIONS (Top View)

#### BLOCK DIAGRAM

#### PIN NAMES AND PIN DESCRIPTION

V<sub>SS</sub> (Power Supply)

Circuit GND potential

$V_{\mathrm{DD}}$  (Power Supply)

+5V during operation Low power standby pin for TMP8049 RAM

V<sub>CC</sub> (Main Power Supply)

+5V during operation

PROG (Output)

Output strobe for the TMP8243P I/O expander

$P_{10}-P_{17}$  (Input/Output) Port 1

8-bit quasi-bidirectional port (Internal Pullup  $\cong 50 \mbox{K}\Omega$  ).

$P_{20}-P_{27}$  (Input/Output) Port 2

8-bit quasi-bidirectional port (Internal Pullup  $\cong 50 \mbox{K}\Omega$  ).

P20-P23 Contain the four high order program counter bits during an external program memory fetch and serve as a 4-bit I/O expander bus for the TMP8243P.

DB<sub>O</sub> -DB<sub>7</sub> (Input/Output, 3 State)

Ture bidirectional port which can be written or read synchronously using the  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$  strobes. The port can also be statically latched. Contains the 8 low order program counter bits during an external program memory fetch, and receives the addressed instruction under the control of  $\overline{\text{PSEN}}$ . Also contains the address and data during an external RAM data store instruction, under control of ALE,  $\overline{\text{RD}}$ , and  $\overline{\text{WR}}$ .

To (Input/Output)

Input pin testable using the conditional transfer instructions JTO and JNTO.  $\rm T_{\rm O}$  can be designated as a clock output using ENTO CLK instruction.

T<sub>1</sub> (Input)

Input pin testable using the JT1 and JNT1 instruction. Can be designated the event counter input using the timer/STRT CNT instruction.

INT (Input)

External interrupt input. Initiates an interrupt if interrupt is enabled. Interrupt is disabled after a reset. Also testable with conditional jump instruction. (Active Low)

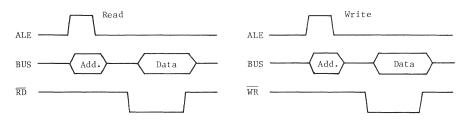

RD (Output)

Output strobe activated during a Bus read. Can be used to enable data onto the Bus from an external device. Used as a Read Strobe to External Data Memory (Active Low).

WR (Output)

Output strobe during a Bus write (Active Low) Used as a Write Strobe to External Data Memory.

#### RESET (Input)

Active Low signal which is used to initialize the Processor. Also used during Power down.

#### ALE (Output)

Address Latch Enable. This signal occurs once during each cycle and is useful as a clock output. The negative edge of ALE strobes address into external data and program memory.

#### PSEN (Output)

Program Store Enable. This output occurs only during a feach to external program memory (Active Low).

#### SS (Input)

Single step input can be used in conjunction with ALE to "single step" processor through each instruction when  $\overline{\rm SS}$  is low the CPU is placed into a wait state after it has completed the instruction being executed.

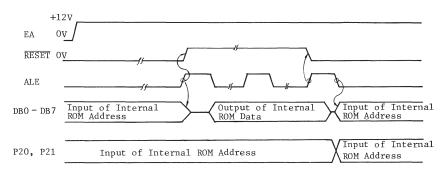

#### EA (Input)

External Access input which forces all program memory fetches to reference external memory. Useful for emulation and debug and essential for testing and program verification. (Active High).

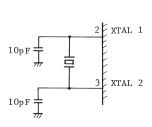

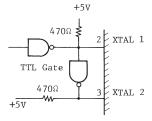

#### XTAL 1 (Input)

One side of crystal input for internal oscillator. Also input for external source.

#### XTAL 2 (Input)

Other side of crystal input.

#### FUNCTIONAL DESCRIPTION

#### 1. System Configuration

The following system functions of the TMP8049 are described in detail.

- (1) Program Memory

- (6) Stack (Stack Pointer)

(2) Data Memory

(7) Flag 0, Flag 1

(3) I/O Port

(8) Program Status Word (PSW)

(4) Timer/Counter

- (9) Reset

- (5) Interrupt Control Circuit

- (10) Oscillator Circuit

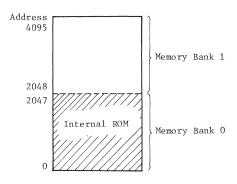

#### (1) Program Memory

• The maximum memory that can be directly addressed by the TMP8049 is 4096 bytes. The first 2048 bytes from location 0 through 2047 can be internal resident mask ROM. The rest of the 2048 bytes of addressable memory are external to the chip. The TMP8039 has no internal resident memory; all memory must be external.

There are three locations in Program Memory of special importance.

Program Memory Area

#### · Location 0

Activating the Reset line of the processor causes the first instruction to be fetched from Location  $0 \cdot$

#### · Location 3

Activating the interrupt line of the processor (if interrupt enabled) causes a jump to subroutine defined by address held in Location  ${\it 3.}$

#### · Location 7

A timer/counter interrupt resulting from a timer/counter overflow (if enabled) causes a jump to a subroutine defined by address held in Location  $7 \cdot$

$\cdot$  Program addresses 0-2047 and 2048-4095 are called memory banks 0 and 1 respectively. Switching of memory banks is achieved by changing the most significant bit of the program counter (PC) during execution of an unconditional jump instruction or call instruction executed after using SEL MBO or SEL MBI.

Reset operation automatically selects Bank 0.

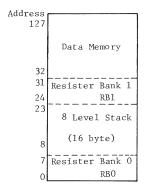

#### (2) Data Memory

- . Resident Data Memory (volatile RAM) is organized as 128 words by 8-bits wide.

- The first 8 locations (0-7) of the memory array are designated as working registers and are directly addressable by several instructions. By executing a Register Bank switch instruction (SEL RB1) locations 24-31 are designated as the working registers in place of 0-7.

Internal Data Memory Area

- RAM locations 8 23 serve a dual role in that they contain the program counter stack which is a stack 2 bytes wide by 8 levels deep. These locations store returning addresses from subroutines. If the level of subroutine nesting is less than the permitted 8, you free up 2 bytes of RAM for general use for every level of nesting not utilized.

- ${\boldsymbol \cdot}$  ALL 128 locations are indirectly addressable through either of two RAM Pointer Registers which reside at RO and R1 of the Register array.

- $\cdot$  The TMP8049 architecture allows extension of the Data Memory to 256 words.

#### (3) Input/Output Ports

- The TMP8049 has 27 I/O lines which can be used for either input or output. These I/O lines are grouped into 3 ports each having 8 bidirectional lines and 3 "test" inputs which can alter program sequences when tested by conditional jump instructions.

- · Ports 1 and 2 are each 8-bits wide and have identical characteristics. Data written to these ports is statically latched and remains unchanged until rewritten. As input ports these lines are non-latching, i.e., inputs must be present until read by an input instruction.

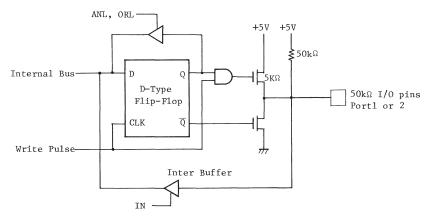

- · All lines of Ports 1 and 2 are called quasi-bidirectional because of a special output circuit structure (illustrated in Figure 1). Each line is continously pulled to a +5V level through a high impedance resistive device  $(50 \mathrm{K}\,\Omega)$  which is sufficient to provide the source current for a TTL high level yet can be pulled low by a standard TTL gate thus allowing the same pin to be used for both input and output. In order to speed up the "0" to "1" transition a low impedance device  $(5 \mathrm{K}\,\Omega)$  is switched in momentarily whenever a "1" is written to line. When a "0" is written to line a low impedance device overcomes the pullup and provides TTL current sinking capability.

Fig.1 Input/Output Circuit of Port 1, Port 2

- . Reset initializes all lines to a high impedance "l" state.

- When external data memory area is not addressed during execution of an internal program, Port 0 (DBO DB7) becomes a true bidirectional port (bus) with associated input and output strobes. If bidirectional feature not needed Bus can serve as either a statically latched output port or a non-latched input port. However, I/O lines of this port cannot be intermixed.

- As a static port data is written and latched using the OUTL instruction and inputted using the INS instruction these two commands generate pulses on the corresponding  $\overline{\text{ND}}$  and  $\overline{\text{WR}}$  strobe lines.

- As a bidirectional port the  $\overline{MOVX}$  instructions are used to read and write the port which generate the  $\overline{WR}$   $\overline{RD}$  strobes.

- $\boldsymbol{\cdot}$  When not being written or read, the Bus lines are in a high impedance state.

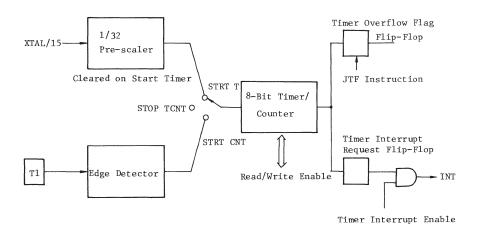

#### (4) Timer/Event Counter

- The 8-bit binary up counter can use either of the following frequency inputs

- (1) Internal clock (1/480 of OSC frequency)

...... Timer mode

## (2) External input clock form T1 terminal (minimum cycle time $3 \times ALE$ cycle)

..... Event Counter mode

The counter is presettable and readable with two MOV instructions which transfer the content of the accumulator to the counter and vice versa. The counter content is not affected by a Reset and is initialized solely by the MOVT, A instruction. The counter is stopped by a Reset or STOP TCNT instruction and remains stopped until started by START T instruction or as an event counter by a START CNT. Once started the counter will increment to its maximum count (FF) and overflow to Zero continuing its count until stopped by a STOP TCNT instruction or

The increment from maximum count to Zero (overflow) results in the setting of an overflow flag and the generation of an interrupt request. When interrupt acknowledged a subroutine call to Location 7 will be initiated. Location 7 should store the starting address of the timer or counter service routine. The state of the overflow flag is testable with the conditional JUMP (JTF). The flag is reset by executing a JTF or by RESET. Figure 2 illustrates the concept of the timer circuit.

Fig. 2 Concept of Timer Circuit

Fig. 3 Concept of Interrupt Control Circuit

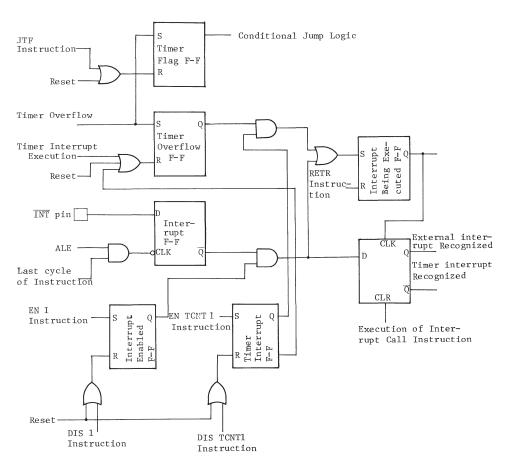

- (5) Interrupt Control Circuit

- . There are two distinct types of Interrupts in the TMP8049.

- (1) External Interrupt from the  $\overline{\text{INT}}$  terminal

- (2) Timer Interrupt caused by timer overflow

The interrupt system is single level in that once an interrupt is detected all further interrupt requests are ignored until execution of an RETR (which should occur at the end of an interrupt service routine) reenables the interrupt input logic.

- An interrupt sequence is initiated by applying a low level "0" to the  $\overline{\text{INT}}$  pin.  $\overline{\text{INT}}$  is level triggered and active low which allows "Wire Oring" of several interrupt sources. The interrupt level is sampled every machine cycle during ALE and when detected causes a "jump to subroutine" at Location 3. As in any call to subroutine, the Program Counter and Program Status Word are saved in the stack.

- . When an overflow occurs in the internal timer/event counter an interrupt request is generated which is reserviced as outlined in previous paragraph except that a jump to Location 7 is used instead of  $\frac{3}{100}$ . If  $\overline{100}$  and times overflow occur simultaneously then external request  $\overline{100}$  takes precedence.

- If an extra external interrupt is needed in addition to  $\overline{\text{INT}}$  this can be achieved by enabling the counter interrupt, loading FFH in the counter (one less than the terminal count), and enabling the event counter mode. A "1" to "0" transition on Tl will cause an interrupt vector to Location 7.

- The interrupt service routine pointed to be addresses in Location 3 or 7 must reside in memory between 0 and 2047, i.e., Bank 0.

Figure 3 illustrates the concept of the interrupt control circuit.

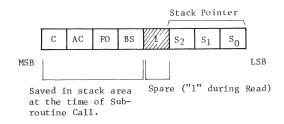

#### (6) Stack (stack Pointer)

- An interrupt or Call to a subroutine causes the contents of the program counter to be stored in one of the 8 register pairs of the Program Counter Stack. The pair to be used is determined by a 3-bit stack pointer which is part of the Program Status Word (PSW explained in section (8)). Data RAM locations, 8 through 23 are available as stack registers and are used to store the program counter and 4-bits of PSW as shown in the figure.

- The stack pointer when initialized points to RAM locations 8 and 9. The first subroutine jump or interrupt results in the program counter contents being transferred to Locations 8 and 9. Then the stack pointer is incremented by one to point to Locations 10 and 11. Eight levels of subroutine are obviously possible.

- At the end of a subroutine signalled by a RET or RETR causes the stack pointer to be decremented by one and the contents of the resulting pair to be transferred to the Program Counter.

| MCU4 | 8-4 | 3 |

|------|-----|---|

|------|-----|---|

#### (7) Flag 0, Flag 1, (F0, F1)

- $\bullet$  The TMP8049 has two flags F0 and F1 which are used for conditional jump. These flags can be set, reset and tested with the conditional jump instruction JF0.

- . FO is a part of the program status word (PSW) and is saved in the stack area when a subroutine is called.

#### (8) Program Status Word (PSW)

• An 8-bit status word which can be loaded to and from the accumulator exsists called the Program Status Word (PSW). The PSW is read by a MOV A, PSW and written to by a MOV PSW, A. The information available in the PSW is shown in the diagram below.

Bits 0 - 2: Stack Pointer Bits(S<sub>0</sub>, S<sub>1</sub>, S<sub>2</sub>)

Bit 3 : Not used ("1" level when read.)

Bit 4 : Working Register Bank Switch Bit

(BS)

0 = Bank 0

1 = Bank 1

Bit 5 : Flag 0 (FO)

Bit 6 : Auxiliary Carry (AC) carry bit generated by an ADD

instruction and used by the decimal adjust instruction

DA, A (AC)

Bit 7 : Carry (C) flag which indicates that the previous

operation has resulted in the accumulator.

(C)

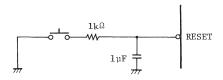

#### (9) Reset

• The reset input provides a means for initialization of the processor. This Schmitt trigger input has an internal pullup resistor which in combination with an external  $1\mu F$  capacitor provides an internal reset pulse sufficient length to guarantee that all internal logic is initialized.

If the pulse is generated externally the reset pin must be held at ground  $(\leq 0.5 \text{V})$  for at least 50mS after the power supply is within tolerance.

Reset performs the following functions within the chip:

- (i) Sets PC to Zero.

- (ii) Sets Stack Pointer to Zero.

- (iii) Selects Register Bank 0.

- (iv) Selects Memory Bank 0.

- (v) Sets BUS (DBO - DB7) to high impedance state. (Except when EA = 5V)

- (vi) Sets Ports 1 and 2 to input mode.

- (vii) Disables interrupts (timer and external).

- (viii) Stops Timer.

- (ix) Clears Timer Flag.

- (x) Clears FO and F1.

- (xi) Disables clock output

#### т0.

#### (10) Oscillator Circuit

• TMP8049 can be operated by the external clock input in addition to crystal oscillator as shown below.

#### 2. Basic Operation and Timing

The following basic operations and timing are explained

- (1) Instruction Cycle

- (2) External Memory Access Timing

- (3) Interface with I/O Expander TMP8243P

- (4) Internal Program Verify (Read) Timing

- (5) Single Step Operation Timing

- (6) Low Power Stand-by Mode

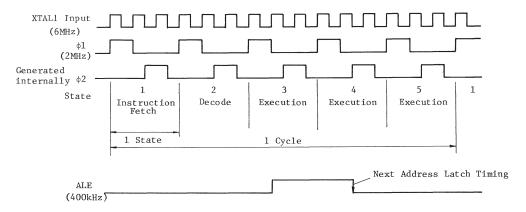

#### (1) Instruction Cycle

- ${\boldsymbol{\cdot}}$  The instructions of TMP8049 are executed in one or two machine cycles, and one machine cycle consists of five states.

- · Fig. 4 illustrates its relationship with the clock input to CPU.

- $\bullet$   $\phi 2$  clock shown in Fig.4 is derived to outside by ENTO CLK instruction.

- ALE can be also used as the clock to indicate the machine cycle as well as giving the external address latch timing.

#### (2) External Memory Access Timing

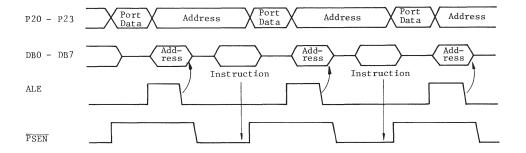

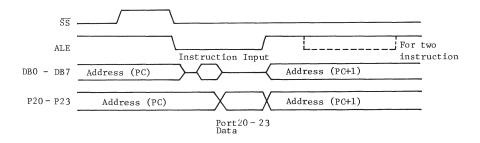

- (i) Program Memory Access

- · TMP8049 programs are executed in the following three modes.

- (1) Execution of internal program only.

- (2) Execution of both external and internal programs.

- (3) Execution of external program only.

The external program memory is accessed (instructions are fetched) automatically when the internal ROM address is exceeded in mode (2) and from initial start address 0 in mode (3).

- · In the external program memory access operation, the following will occur

- . The contents of the 12-bit program counter will be output on BUS(DBO DB7) and the lower 4-bits of Port 2.

- · Address Latch Enable (ALE) will indicate the time at which address is valid. The trailing edge of ALE is used to latch the address externally.

- Program Store Enable (PSEN) indicates that an external instruction fetch is in progress and serves to enable the external memory device.

- BUS (DBO DB7) reverts to Input mode and the processor accepts its 8-bit contents as an Instruction Word.

- $\boldsymbol{\cdot}$  Figure 5 illustrates the timing.

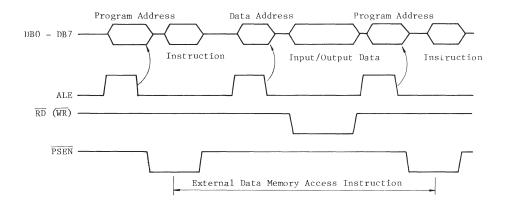

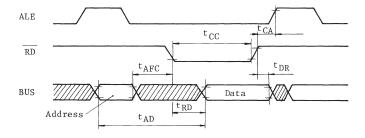

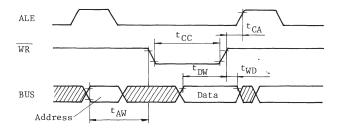

- (ii) Access of External Data Memory

- $\bullet$  In the extended data memory access operation during READ/WRITE cycle the following occurs

- . The contents of RO R1 is output onto BUS (DBO DB7).

- $\bullet$  ALE indciates address is valid. The trailing edge of ALE is used to latch the address externally.

- A read  $\overline{RD}$  or write  $\overline{WR}$  pulse on the corresponding output pins indicates the type of data memory access in progress. Output data valid at trailing edge of  $\overline{WR}$  and input data must be valid at trailing edge of  $\overline{RD}$ .

- · Data (8-bits) is transferred over BUS.

Fig.4 Instruction Cycle Timing

Fig.5 Timing of External Program Memory Access

Suggest we have two diagrams

Fig. 6 Timing of Accessing External Data Memory

- Figure 6 illustrates the timing of accessing the external data memory during execution of external program.

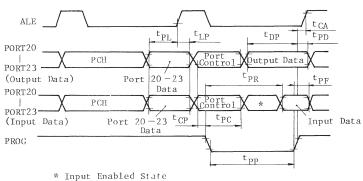

- (3) Interface with I/O Expander (TMP8243P)

- The TMP8049 I/O can be easily expanded using the TMP8243 I/O Expander. This device uses only the lower half 4-bits of Port 2 for communication with the TMP8049. The TMP8243 contains four 4-bit I/O ports which serve as extensions of one chip I/O and are addressed as Ports (4-7). All communication takes place over the lower half of Port 2 (P2O P23) with timing provided by an output pulse on the PROG pin. Each transfer consists of two 4-bit nibbles the first containing the "OP Code" and port address and the second containing the actual 4-bits of data.

Fig. 7 Timing of Rading Internal Program Memory

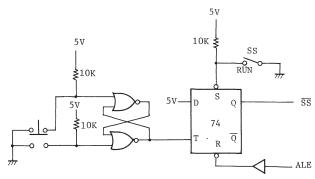

Fig.8(a) Single Step Circuit

#### (4) Reading of Internal Program Memory

- The processor is placed in the READ mode by applying +12V to the EA pin and OV to the RESET pin. The address of the location to be read is then applied to BUS and the low order 2-bits of Port 2. The address is latched by a 0 to 1 transition on RESET and the high level causes the contents of program memory location addressed to appear on the eight lines of BUS.

- · Figure 7 illustrates the timing diagram for this operation.

#### (5) Single Step Operation.

- A single step feature useful for debug can be implemented by utilizing a circuit shown in Figure 8 (a) combined with the SS pin and ALE pin.

- · A D-type flip flop with set and reset is used to generate  $\overline{SS}$ . In the run mode  $\overline{SS}$  is held high by keeping the flip flop set. To enter single step, set is removed allowing ALE to bring  $\overline{SS}$  low via reset input. The next instruction is started by clocking a "1" into the FF which will not appear on  $\overline{SS}$  unless ALE is high removing reset. In response to SS going high the processor begins an instruction fetch which brings ALE low resetting FF and causing the processor to again enter the stopped state.

- The timeing deagram in this case is as shown in Figure 8 (b). (EA = 5V).

#### (6) Lower Power Stand-by Mode.

• The TMP8049 has been organized to allow power to be removed from all but the volatile,  $128\times8$  data RAM array. In power down mode the contents of data RAM can be maintained while drawing typically 10 - 15% of normal operating power requirements.

VCC serves as the 5V supply for the bulk of the TMP8049 while the VDD supplies only the RAM array. In standby mode VCC is reduced to 0V but  $\rm V_{DD}$  is kept at 5V. Applying a low level to reset inhibits any access to the RAM by the processor and guarantees that RAM cannot be inadvertently altered as power is removed from VCC.

Fig.8(b) Single Step Operation Timing

INSTRUCTION

ACCUMULATOR INSTRUCTION

| Mnemonic     |         |         | In      | struc   | tion    | Code    |         |         |                                                  |       |        | F] | ag |

|--------------|---------|---------|---------|---------|---------|---------|---------|---------|--------------------------------------------------|-------|--------|----|----|

| rmemonic     | D7      | D6      | D5      | D4      | D3      | D2      | D1      | DO      | Operation                                        | Bytes | Cycles | С  | AC |

| ADD A,Rr     | 0       | 1       | 1       | 0       | 1       | r       | r       | r       | $(A)^{\prec}(A) + (Rr)$<br>r = 0 - 7             | 1.    | 1      | 0  | 0  |

| ADD A,@Rr    | 0       | 1       | 1       | 0       | 0       | 0       | 0       | r       | $(A) \leftarrow (A) + (Rr)$<br>r = 0, 1          | 1     | 1      | 0  | 0  |

| ADD A,#Data  | 0<br>d7 | 0<br>d6 | 0<br>d5 | 0<br>d4 | 0<br>d3 | 0<br>d2 | 1<br>d1 | 1<br>d0 | (A) (A)+Data                                     | 2     | 2      | 0  | 0  |

| ADDC A,Rr    | 0       | 1       | 1       | 1       | 1       | r       | r       | r       | $(\Lambda) < (\Lambda) + (Rr) + (C)$ $r = 0 - 7$ | 1     | 1      | 0  | 0  |

| ADDC A,@Rr   | 0       | 1       | 1       | 1       | 0       | 0       | 0       | r       | $(A) \cdot (A) + ((Rr)) + (C)$<br>r = 0, 1       | 1     | 1      | 0  | 0  |

| ADDC A,#Data | 0<br>d7 | 0<br>d6 | 0<br>d5 | 1<br>d4 | 0<br>d3 | 0<br>d2 | 1<br>d1 | 1<br>d0 | (A) (Λ)+Data+(C)                                 | 2     | 2      | 0  | 0  |

| ANL A,Rr     | 0       | 1       | 0       | 1       | 1       | r       | r       | r       | $(A) \leftarrow (A) \land (Rr)$ $r = 0 - 7$      | 1     | 1      | -  | -  |

| ANL A,@Rr    | 0       | 1       | 0       | 1       | 0       | 0       | 0       | r       | $(A) \leftarrow (A) \wedge ((Rr))$ $r = 0, 1$    | 1     | 1      | -  | -  |

| ANL A,#Data  | 0<br>d7 | 1<br>d6 | 0<br>d5 | 1<br>d4 | 0<br>d3 | 0<br>d2 | 1<br>d1 | 1<br>d0 | (A)≺(A)∧Data                                     | 2     | 2      | -  | -  |

| ORL A,Rr     | 0       | 1       | 0       | 0       | 1       | r       | r       | r       | $(A) \leftarrow (A) \lor (Rr)$ $r = 0 - 7$       | 1     | 1      | -  | -  |

| ORL A,@Rr    | 0       | 1       | 0       | 0       | 0       | 0       | 0       | r       | $(A) \leftarrow (A) \lor ((Rr))$ $r = 0, 1$      | 1     | 1      | -  | -  |

| ORL A,#Data  | 0<br>d7 | 1<br>d6 | 0<br>d5 | 0<br>d4 | 0<br>d3 | 0<br>d2 | 1<br>d1 | 1<br>d0 | (A)←(A)∨Data                                     | 2     | 2      | -  | -  |

| XRL A,Rr     | 1       | 1       | 0       | 1       | 1       | r       | r       | r       | $(A) \leftarrow (A) \forall (Rr)$ $r = 0 - 7$    | 1     | 1      | -  | -  |

| XRL A,@Rr    | 1.      | 1       | 0       | 1       | 0       | 0       | 0       | r       | $(A) \leftarrow (A) \forall ((Rr))$ $r = 0, 1$   | 1     | 1      | -  | -  |

| XRL A,#Data  | 1<br>d7 | 1<br>d6 | 0<br>d5 | 1<br>d4 | 0<br>d3 | 0<br>d2 | 1<br>d1 | 1<br>d0 | (A)←(A)∀Data                                     | 2     | 2      | -  | -  |

| INC A        | 0       | 0       | 0       | 1       | 0       | 1       | 1       | 1       | (A) ← (A) +1                                     | 1     | 1      | -  | -  |

| DEC A        | 0       | 0       | 0       | 0       | 0       | 1       | 1       | 1       | (A)←(A)-1                                        | 1     | 1      | -  | -  |

| CLR A        | 0       | 0       | 1       | 0       | 0       | 1       | 1       | 1       | (A)←0                                            | 1     | 1      | -  | -  |

| CPL A        | 0       | 0       | 1       | 1       | 0       | 1       | 1       | 1       | (A)←NOT (A)                                      | 1     | 1      | -  | -  |

| DA A         | 0       | 1       | 0       | 1       | 0       | 1       | 1       | 1       | Decimal Adjust<br>Accumulator                    | 1     | 1      | 0  | -  |

| SWAP A       | 0       | 1       | 0       | 0       | 0       | 1       | 1       | 1       | (A4-7) <del></del> ←(A0-3)                       | 1     | 1      | -  | -  |

| Mnemonic |    |    | Inst | ruct | ion C | ode |    |    | Operation                                                             | Rutos | Cycles |   | ag |

|----------|----|----|------|------|-------|-----|----|----|-----------------------------------------------------------------------|-------|--------|---|----|

| rmemonic | D7 | D6 | D5   | D4   | D3    | D2  | D1 | DO | Operation                                                             | bytes | Cycles | С | AC |

| RL A     | 1  | 1  | 1    | 0    | 0     | 1   | 1  | 1  | $(\Lambda n+1) < (\Lambda n)$ $n = 0 - 6$ $(\Lambda 0) < (\Lambda 7)$ | 1     | 1      | - | -  |

| RLC A    | 1  | 1  | 1    | 1    | 0     | 1   | 1  | 1  | (An+1) ← (An)<br>n = 0 - 6<br>(C) ← (A7)<br>(A0) ← (C)                | 1     | 1      | - | _  |

| RR A     | 0  | 1  | 1    | 1    | 0     | 1   | 1  | 1  | (An) < (An+1)<br>n = 0 - 6<br>(A7) ← (A0)                             | 1     | 1      | - | _  |

| RRC A    | 0  | 1  | 1    | 0    | 0     | 1   | 1  | 1  | (An) ← (An+1)<br>n = 0 - 6<br>(C) ← (A0)<br>(A7) ← (C)                | 1     | 1      | - | _  |

#### Input/Output Instruction

|                |         |         | Inst    | ruct    | ion C   | ode     |         |         |                                      |       | 0 1    | F | lag |

|----------------|---------|---------|---------|---------|---------|---------|---------|---------|--------------------------------------|-------|--------|---|-----|

| Mnemonic       | D7      | D6      | D5      | D4      | D3      | D2      | D1      | DO      | Operation                            | Bytes | Cycles | Α | AC  |

| IN A,Pp        | 0       | 0       | 0       | 0       | 1       | 0       | P       | Р       | (A) + (Pp)<br>P = 1, 2               | 1     | 2      | - | -   |

| OUTL Pp,A      | 0       | 0       | 1       | 1       | 1       | 0       | P       | Р       | $(Pp) \leftarrow (A)$<br>P = 1, 2    | 1     | 2      | - | -   |

| ANL Pp,#Data   | 1<br>d7 | 0<br>d6 | 0<br>d5 | 1<br>d4 | 1<br>d3 | 0<br>d2 | P<br>dl | P<br>d0 | (Pp)←(Pp)∧Data<br>P = 1, 2           | 2     | 2      | - | -   |

| ORL Pp,#Data   | 1<br>d7 | 0<br>d6 | 0<br>d5 | 0<br>d4 | 1<br>d3 | 0<br>d2 | P<br>d1 | P<br>d0 | (Pp)←(Pp)VData<br>P = 1, 2           | 2     | 2      | - | -   |

| INS A, BUS     | 0       | 0       | 0       | 0       | 1       | 0       | 0       | 0       | (A)←(BUS)                            | 1     | 2      | - | -   |

| OUTL BUS,A     | 0       | 0       | 0       | 0       | 0       | 0       | 1       | 0       | (BUS)←(A)                            | 1     | 2      | - | -   |

| ANL BUS, #Data | 1<br>d7 | 0<br>d6 | 0<br>d5 | 1<br>d4 | 1<br>d3 | 0<br>d2 | 0<br>d1 | 0<br>d0 | (BUS)÷(BUS)∧Data                     | 2     | 2      | - | -   |

| ORL BUS,#Data  | 1<br>d7 | 0<br>d6 | 0<br>d5 | 0<br>d4 | 1<br>d3 | 0<br>d2 | 0<br>d1 | 0<br>d0 | (BUS)←(BUS)∨Data                     | 2     | 2      | - | -   |

| MOVD A, Pp     | 0       | 0       | 0       | 0       | 1       | 1       | P       | P       | (A0-3)←(Pp)<br>(A4-7)←0<br>P = 4 - 7 | 1     | 2      | - | -   |

| MOVD Pp,A      | 0       | 0       | 1       | 1       | 1       | 1       | P       | Р       | $(Pp) \leftarrow (A0-3)$<br>P = 4-7  | 1     | 2      | - | -   |

MCU48-53

| Mnemonic  |    |    | Inst | ructi | on Co | de |    |    | 0                                              | n .   | 0 1    | F1 | ag |

|-----------|----|----|------|-------|-------|----|----|----|------------------------------------------------|-------|--------|----|----|

| Miemonic  | D7 | D6 | D5   | D4    | D3    | D2 | D1 | D0 | Operation                                      | Bytes | Cycles | С  | AC |

| ANLD Pp,A | 1  | 0  | 0    | 1     | 1     | 1  | P  | P  | $(Pp) \leftarrow (Pp) \land (A0-3)$ $P = 4-7$  | 1     | 2      | -  | -  |

| ORLD Pp,A | 1  | 0  | 0    | 0     | 1     | 1  | P  | P  | $(Pp) \leftarrow (Pp) \lor (A0-3)$ $P = 4 - 7$ | 1     | 2      | -  | -  |

#### Register Instruction

| Mnemonic  |    |    | Inst | ruct | ion ( | ode |    |    | Operation                                  | Prot o o | Cycles | F1 | ag |

|-----------|----|----|------|------|-------|-----|----|----|--------------------------------------------|----------|--------|----|----|

| Thremonic | D7 | D6 | D5   | D4   | D3    | D2  | D1 | DO | Operacion                                  | bytes    | cycles | С  | AC |

| INC Rr    | 0  | 0  | 0    | 1    | 1     | r   | r  | r  | (Rr)←(Rr)+1<br>r = 0 - 7                   | 1        | 1      | -  | -  |

| INC @Rr   | 0  | 0  | 0    | 1    | 0     | 0   | 0  | r  | $((Rr)) \leftarrow ((Rr)) + 1$<br>r = 0, 1 | 1        | 1      | -  | -  |

| DEC Rr    | 1  | 1  | 0    | 0    | 1     | r   | r  | r  | $(Rr) \leftarrow (Rr) - 1$ $r = 0 - 7$     | 1        | 1      | -  | -  |

#### Branch Instruction

| Mnemonic            |           |          | Inst     | ruct    | ion C   | ode     |         |         | Operation                                                            | Bytes | Cycles | F1 | ag |

|---------------------|-----------|----------|----------|---------|---------|---------|---------|---------|----------------------------------------------------------------------|-------|--------|----|----|

|                     | D7        | D6       | D5       | D4      | D3      | D2      | D1      | D0      |                                                                      |       | -,     | С  | AC |

| JMP Address         | a10<br>a7 | a9<br>a6 | a8<br>a5 | 1<br>a4 | 0<br>a3 | 1<br>a2 | 0<br>a1 | 0<br>a0 | (PCO-7)←(aO-7)<br>(PC8-10)←(a8-10)<br>(PC11)←DBF                     | 2     | 2      | -  | _  |

| JMPP @A             | 1         | 0        | i        | 1       | 0       | 0       | 1       | 1       | (PCO-7)←((A))                                                        | 1     | 2      | -  | -  |

| DJNZ Rr,<br>Address | 1<br>a7   | 1<br>a6  | 1<br>a5  | 0<br>a4 | 1<br>a3 | r<br>a2 | r<br>al | r<br>a0 | (Rr)←(Rr)-1<br>if Rr not 0<br>(PCO-7)←(aO-7)                         | 2     | 2      | _  | -  |

| JC Address          | 1<br>a7   | 1<br>a6  | 1<br>a5  | 1<br>a4 | 0<br>a3 | 1<br>a2 | l<br>al | 0<br>a0 | $(PC0-7) \leftarrow (a0-7)$<br>if C = 1<br>(PC) = (PC)+2<br>if C = 0 | 2     | 2      | -  | -  |

| JNC Address         | 1<br>a7   | 1<br>a6  | 1<br>a5  | 0<br>a4 | 0<br>a3 | 1<br>a2 | l<br>al | 0<br>a0 | (PCO-7)←(aO-7)<br>if C = 0<br>(PC)←(PC)+2<br>if C = 1                | 2     | 2      | -  | _  |

|              |          |          | Inst     | ructi   | ion     |         |         |         |                                                                                                        |       |        | F1 | ag |

|--------------|----------|----------|----------|---------|---------|---------|---------|---------|--------------------------------------------------------------------------------------------------------|-------|--------|----|----|

| Mnemonic     | D7       | D6       | D5       | D4      | D3      | D2      | D1      | DO      | Operation                                                                                              | Bytes | Cycles | С  | AC |

| JZ Address   | 1<br>a7  | 1<br>a6  | 0<br>a5  | 0<br>a4 | 0<br>a3 | 1<br>a2 | 1<br>al | 0<br>a0 | $(PC0-7) \leftarrow (a0-7)$<br>if $(A) = 0$<br>$(PC) \leftarrow (PC) + 2$<br>if $(A) \neq 0$           | 2     | 2      | -  | _  |

| JNZ Address  | 1<br>a7  | 0<br>a6  | 0<br>a5  | 1<br>a4 | 0<br>a3 | 1<br>a2 | 1<br>al | 0<br>a0 | $(PCO-7) \leftarrow (aO-7)$<br>if (A) \( \frac{1}{2} \) 0<br>$(PC) \leftarrow (PC) + 2$<br>if (A) = 0  | 2     | 2      | -  | -  |

| JTO Address  | 0<br>a7  | 0<br>a6  | 1<br>a5  | 1<br>a4 | 0<br>a3 | 1<br>a2 | 1<br>al | 0<br>a0 | (PCO-7)←(aO-7)<br>if TO = 1<br>(PC)←(PC)+2<br>if TO = 0                                                | 2     | 2      | -  | _  |

| JNTO Address | 0<br>a7  | 0<br>a6  | 1<br>a5  | 0<br>a4 | 0<br>a3 | 1<br>a2 | l<br>al | 0<br>a0 | (PCO-7)←(aO-7)<br>if TO = 0<br>(PC)←(PC)+2<br>if TO = 1                                                | 2     | 2      | -  | _  |

| JT1 Address  | 0<br>a7  | 1<br>a6  | 0<br>a5  | 1<br>a4 | 0<br>a3 | 1<br>a2 | l<br>al | 0<br>a0 | (PCO-7)←(aO-7)<br>if T1 = 1<br>(PC)←(PC)+2<br>if T1 = 0                                                | 2     | 2      | -  | -  |

| JNT1 Address | 0<br>a7  | 1<br>a6  | 0<br>a5  | 0<br>a4 | 0<br>a3 | 1<br>a2 | 1<br>al | 0<br>a0 | $(PC0-7) \leftarrow (a0-7)$<br>if T1 = 0<br>$(PC) \leftarrow (PC) + 2$<br>if T1 = 1                    | 2     | 2      | -  | -  |

| JFO Address  | 1<br>a7  | 0<br>a6  | 1<br>a5  | 1<br>a4 | 0<br>a3 | 1<br>a2 | l<br>al | 0<br>a0 | $(PCO-7) \leftarrow (aO-7)$<br>if FO = 1<br>$(PC) \leftarrow (PC)+2$<br>if FO = 0                      | 2     | 2      | -  | -  |

| JFl Address  | 0<br>a7  | 1<br>a6  | 1<br>a5  | 1<br>a4 | 0<br>a3 | 1<br>a2 | l<br>al | 0<br>a0 | $(PC0-7) \leftarrow (a0-7)$<br>if F1 = 1<br>$(PC) \leftarrow (PC) + 2$<br>if F1 = 0                    | 2     | 2      | -  | _  |

| JTF Address  | 0<br>a7  | 0<br>a6  | 0<br>a5  | 1<br>a4 | 0<br>a3 | 1<br>a2 | l<br>al | 0<br>a0 | (PCO-7)+(aO-7)<br>if TF = 1<br>(PC)+(PC)+2<br>if TF = 0                                                | 2     | 2      | -  | -  |

| JN1 Address  | 1<br>a7  | 0<br>a6  | 0<br>a5  | 0<br>a4 | 0<br>a3 | 1<br>a2 | 1<br>al | 0<br>a0 | $(PCO-7) \leftarrow (aO-7)$<br>if INT = 0<br>$(PC) \leftarrow (PC) + 2$<br>if INT = 1                  | 2     | 2      | -  | _  |

| JBb Address  | b2<br>a7 | b1<br>a6 | b0<br>a5 | 1<br>a4 | 0<br>a3 | 0<br>a2 | l<br>al | 0<br>a0 | $(PCO-7) \leftarrow (aO-7)$<br>if $Bb = 1$<br>$(PC) \leftarrow (PC) + 2$<br>if $Bb = 0$<br>(b = 0 - 7) | 2     | 2      | -  | _  |

MCU48-55

#### Subroutine Instruction

| Mnemonics    |           |          | Ins      | truct   | ion (   | Code    |         |         | Operation                                                                                   | Parton | Cycles | F1 | ag |

|--------------|-----------|----------|----------|---------|---------|---------|---------|---------|---------------------------------------------------------------------------------------------|--------|--------|----|----|

| Tinelionites | D7        | D6       | D5       | D4      | D3      | D2      | D1      | DO      | Operation                                                                                   | bytes  | Cycles | С  | AC |

| CALL Address | a10<br>a7 | a9<br>a6 | a8<br>a5 | 1<br>a4 | 0<br>a3 | 1<br>a2 | 0<br>a1 | 0<br>a0 | ((SP))←<br>(PC),(PSW4-7)<br>(SP)←(SP)+1<br>(PC8-10)←(a8-10)<br>(PC0-7)←(a0-7)<br>(PC11)←DBF | 2      | 2      | _  | _  |

| RET          | 1         | 0        | 0        | 0       | 0       | 0       | 1       | 1       | (SP)+(SP)-1<br>(PC)+((SP))                                                                  | 1      | 2      | -  | -  |

| RETR         | 1         | 0        | 0        | 1       | 0       | 0       | 1       | 1       | (SP)←(SP)-1<br>(PC)←((SP))<br>(PSW4-7)←((SP))                                               | 1      | 2      | -  | -  |

#### Flag Manipulation Instruction

| Mnemonics |    |    | Ins | truct | ion ( | Code |    |    | Operation       | Bytes | Cycles | F1 | ag |

|-----------|----|----|-----|-------|-------|------|----|----|-----------------|-------|--------|----|----|

| rmemonics | D7 | D6 | D5  | D4    | D3    | D2   | D1 | DO | operation       | bytes | Cycles |    | AC |

| CLR C     | 1  | 0  | 0   | 1     | 0     | 1    | 1  | 1  | (c)←0           | 1     | 1      | 0  | _  |

| CPL C     | 1  | 0  | 1   | 0     | 0     | 1    | 1  | 1  | (C)←NOT(C)      | 1     | 1      | 0  | -  |

| CLR FO    | 1  | 0  | 0   | 0     | 0     | 1    | 0  | 1  | (FO)←0          | 1     | 1      | -  | -  |

| CPL FO    | 1  | 0  | 0   | 1     | 0     | 1    | 0  | 1  | (FO)←NOT(FO)    | 1     | 1      | -  | -  |

| CLR F1    | 1  | 0  | 1   | 0     | 0     | 1    | 0  | 1  | (F1)←0          | 1     | 1      | -  | -  |

| CPL F1    | 1  | 0  | 1   | 1     | 0     | 1    | 0  | 1  | (F1) ← NOT (F1) | 1     | 1      | -  | -  |

|           | 1  | 1  | 1   | 1     | 1     | 1    | 1  |    | 1               | 1     | 1      |    | 1  |

#### Data Transter Instruction

| Mnemonics   |         |         | Ins     | truct   | ion (   | ode     |         |         | Operation                           | Bytes | Cycles | F1 | ag |

|-------------|---------|---------|---------|---------|---------|---------|---------|---------|-------------------------------------|-------|--------|----|----|

| THICHIOTIES | D7      | D6      | D5      | D4      | D3      | D2      | D1      | DO      | operación                           |       | 5,0100 | С  | AC |

| MOV A,Rr    | 1       | 1.      | 1       | 1       | 1       | r       | r       | r       | (A)←(Rr)<br>r = 0 - 7               | 1     | 1      | -  | -  |

| MOV A,@Rr   | 1       | 1       | 1       | 1       | 0       | 0       | 0       | r       | $(A) \leftarrow ((Rr))$<br>r = 0, 1 | 1     | 1      | -  | -  |

| MOV A,#Data | 0<br>d7 | 0<br>d6 | 1<br>d5 | 0<br>d4 | 0<br>d3 | 0<br>d2 | 1<br>d1 | 1<br>d0 | (A)←Data                            | 2     | 2      | -  | -  |

| MOV Rr,A    | 1       | 0       | 1       | 0       | 1       | r       | r       | r       | $(Rr) \leftarrow (A)$ $r = 0 - 7$   | 1     | 1      | _  | -  |

| Mnemonics     |         |         | Ins     | truc    | tion    | Code    |         |         | 0                                                                 | D     | Cvcles | F1 | ag |

|---------------|---------|---------|---------|---------|---------|---------|---------|---------|-------------------------------------------------------------------|-------|--------|----|----|

| mnemonics     | D7      | D6      | D5      | D4      | D3      | D2      | D1      | D0      | Operation                                                         | Bytes | Cycles | С  | AC |

| MOV @Rr,A     | 1       | 0       | 1       | 0       | 0       | 0       | 0       | r       | $((Rr))^{\prec}(A)$<br>r = 0, 1                                   | 1     | 1      | -  | -  |

| MOV Rr,#Data  | 1<br>d7 | 0<br>d6 | 1<br>d5 | 1<br>d4 | 1<br>d3 | r<br>d2 | r<br>dl | r<br>d0 | (Rr)←Data<br>r = 0 - 7                                            | 2     | 2      | -  | -  |

| MOV @Rr,#Data | 1<br>d7 | 0<br>d6 | 1<br>d5 | 1<br>d4 | 0<br>d3 | 0<br>d2 | 0<br>d1 | r<br>d0 | ((Rr))←Data<br>r = 0, 1                                           | 2     | 2      | -  | -  |

| MOV A,PSW     | 1       | 1       | 0       | 0       | 0       | 1       | 1       | 1       | (A) ← (PSW)                                                       | 1     | 1      | -  | -  |

| MOV PSW,A     | 1       | 1       | 0       | 1       | 0       | 1       | 1       | 1       | (PSW)≺(A)                                                         | 1     | 1      | -  | -  |

| XCH A, Rr     | 0       | 0       | 1       | 0       | 1       | r       | r       | r       | $(A) \stackrel{\rightarrow}{\leftarrow} (Rr)$ $r = 0 - 7$         | 1     | 1      | -  | -  |

| XCH A,@Rr     | 0       | 0       | 1       | 0       | 0       | 0       | 0       | r       | $(A) \stackrel{\rightarrow}{\leftarrow} ((Rr))$ $r = 0, 1$        | 1     | 1      | -  | -  |

| XCHD A,@Rr    | 0       | 0       | 1       | 1       | 0       | 0       | 0       | r       | $(A0-3) \stackrel{\rightarrow}{\leftarrow} ((Rr0-3))$<br>r = 0, 1 | 1     | 1      | -  | _  |

| MOVX A,@Rr    | 1       | 0       | 0       | 0       | 0       | 0       | 0       | r       | $(A) \leftarrow ((Rr))$<br>r = 0, 1                               | 1     | 2      | -  | -  |

| MOVX @Rr,A    | 1       | 0       | 0       | 1       | 0       | 0       | 0       | r       | ((Rr)) + (A)<br>r = 0, 1                                          | 1     | 2      | -  | -  |

| MOVP A,@A     | 1       | 0       | 1       | 0       | 0       | 0       | 1       | 1       | (PCO-7)←(A)<br>(A)←((PC))                                         | 1     | 2      | -  | -  |

| MOVP3 A,@A    | 1       | 1       | 1       | 0       | 0       | 0       | 1       | 1       | (PCO-7)←(A)<br>(PC8-11)←0011<br>(A)←((PC))                        | 1     | 2      | -  | -  |

#### Timer/Counter Instruction

| Mnemonics  |    |    | Inst | ruct | ion C | lode |    | *************************************** | Operation                                              | Bytes | s Cycles | Flag |    |

|------------|----|----|------|------|-------|------|----|-----------------------------------------|--------------------------------------------------------|-------|----------|------|----|

| Turemonres | D7 | D6 | D5   | D4   | D3    | D2   | D1 | DO                                      | operation                                              | 2,000 | 0,000    | С    | AC |

| MOV A,T    | 0  | 1  | 0    | 0    | 0     | 0    | 1  | 0                                       | (A)÷(T)                                                | 1     | 1        | -    | -  |

| MOV T,A    | 0  | 1  | 1    | 0    | 0     | 0    | 1  | 0                                       | (T)←(A)                                                | 1     | 1        | -    | -  |

| STRT T     | 0  | 1  | 0    | 1    | 0     | 1    | 0  | 1                                       | Counting is started in the timer mode                  | 1     | 1        | -    | -  |

| STRT CNT   | 0  | 1  | 0    | 0    | 0     | 1    | 0  | 1                                       | Counting is<br>started in the<br>event counter<br>mode | 1     | 1        | -    | -  |

MCU48-57

| Managaria |    | Instruction Code |    |    |    |    |    | Operation | Bytes                                                | Cycles | F1     | ag |    |

|-----------|----|------------------|----|----|----|----|----|-----------|------------------------------------------------------|--------|--------|----|----|

| Mnemonics | D7 | D6               | D5 | D4 | D3 | D2 | D1 | DO        | Operation                                            | Бусеѕ  | Cycles | С  | AC |

| STOP TCNT | 0  | 1                | 1  | 0  | 0  | 1  | 0  | 1         | Stop both time<br>accumulation and<br>event counting | 1      | 1      | _  | -  |

| EN TCNT1  | 0  | 0                | 1  | 0  | 0  | 1  | 0  | 1         | Timer interrupt is enabled                           | 1      | 1      | -  | -  |

| DIS TCNT1 | 0  | 0                | 1  | 1  | 0  | 1  | 0  | 1         | Timer interrupt is disabled                          | 1      | 1      | -  | -  |

#### Control Instruction

| Mnemonics |    |    | Ins | truct | ion | Code |    |    | Operation Bytes                                      |   | Cycles | F1 | ag |

|-----------|----|----|-----|-------|-----|------|----|----|------------------------------------------------------|---|--------|----|----|

|           | D7 | D6 | D5  | D4    | D3  | D2   | D1 | D0 |                                                      |   |        | С  | AC |

| EN I      | 0  | 0  | 0   | 0     | 0   | 1    | 0  | 1  | External inter-<br>rupt is enabled                   | 1 | 1      | _  | -  |

| DIS I     | 0  | 0  | 0   | 1     | 0   | 1    | 0  | 1  | External inter-<br>rupt is disabled                  | 1 | 1      | -  | -  |

| SEL RBO   | 1  | 1  | 0   | 0     | 0   | 1    | 0  | 1  | (BS)←0                                               | 1 | 1      | -  | -  |

| SEL RB1   | 1  | 1  | 0   | 1     | 0   | 1    | 0  | 1  | (BS)←1                                               | 1 | 1      | -  | -  |

| SEL MBO   | 1  | 1  | 1   | 0     | 0   | 1    | 0  | 1  | (DBF)←0                                              | 1 | 1      | -  | -  |

| SEL MB1   | 1  | 1  | 1   | 1     | 0   | 1    | 0  | 1  | (DBF)←1                                              | 1 | 1      | -  | -  |

| ENTO CLK  | 0  | 1  | 1   | 1     | 0   | 1    | 0  | 1  | T <sub>O</sub> is enabled to act as the clock output |   | 1      | -  | -  |

| NOP       | 9  | 0  | 0   | 0     | 0   | 0    | 0  | 0  | No operation                                         | 1 | 1      | -  | -  |

#### TMP8049P/8039P/8049P-6/8039P-6

#### ABSOLUTE MAXIMUM RATINGS

| SYMBOL            | ITEM                                                                            | RATING         |

|-------------------|---------------------------------------------------------------------------------|----------------|

| $v_{\mathrm{DD}}$ | $V_{ m DD}$ Supply Voltage (with respect to GND ( $V_{ m SS}$ ))                | -0.5V to +7V   |

| $v_{CC}$          | $	extsf{VCC}$ Supply Voltage (with respect to GND ( $	extsf{V}_{	extsf{SS}}$ )) | -0.5V to +7V   |

| V <sub>INA</sub>  | Input Voltage (Except EA)                                                       | -0.5V to +7V   |

| V <sub>INB</sub>  | Input Voltage (Only EA)                                                         | -0.5V to +13V  |

| P <sub>D</sub>    | Power Dissipation (Ta=25°C)                                                     | 1.5W           |

| TSOLDER           | Soldering Temperature (Soldering Time 10 sec.)                                  | 260°C          |

| TSTG              | Storage Temperature                                                             | -55°C to 150°C |

| TOPR              | Operating Temperature                                                           | 0°C to 70°C    |

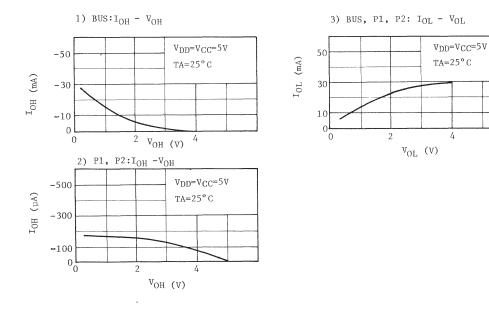

DC CHARACTERISTCS TA=0°C to 70°C,  $v_{CC}=v_{DD}=+5v\pm10\%$ ,  $v_{SS}=0v$ , Unless Otherwise Noted.

| SYMBOL                           | PARAMETER                                                | TEST CONDITIONS                                        | MIN. | TYP. | MAX.            | UNIT |

|----------------------------------|----------------------------------------------------------|--------------------------------------------------------|------|------|-----------------|------|

| $a^{\mathrm{I}\Gamma}$           | Input Low Voltage                                        |                                                        | -0.5 | -    | 0.8             | V    |

| $v_{IH}$                         | Input High Voltage (Except XTAL1, XTAL2, RESET)          |                                                        | 2.0  | -    | VCC             | V    |

| $v_{IH1}$                        | Input High Voltage (XTAL1, XTAL2, RESET)                 |                                                        | 3.8  | _    | v <sub>CC</sub> | V    |

| $v_{\rm OL}$                     | Output Low Voltage (BUS)                                 | IOL=2.0mA                                              | -    | -    | 0.45            | V    |

| $v_{\rm OL1}$                    | Output Low Voltage (RD, WR, PSEN, ALE)                   | I <sub>OL=1.8mA</sub>                                  | _    | -    | 0.45            | V    |

| $v_{\text{OL2}}$                 | Output Low Voltage (PROG)                                | I <sub>OL=1.0mA</sub>                                  | -    | -    | 0.45            | V    |

| v <sub>OL'3</sub>                | Output Low Voltage<br>(For other output pins)            | I <sub>OL=1.6mA</sub>                                  | -    | -    | 0.45            | V    |

| $v_{OH}$                         | Output High Voltage (BUS)                                | I <sub>OH</sub> =-400μA                                | 2.4  | _    | _               | V    |

| V <sub>OH1</sub>                 | Output High Voltage (RD, WR, PSEN, ALE)                  | <sup>I</sup> OH=-100μA                                 | 2.4  | -    | -               | V    |

| v <sub>OH2</sub>                 | Output High Voltage<br>(For tothe output pins)           | Ι <sub>ΟΗ</sub> =-40μΑ                                 | 2.4  | _    | -               | V    |

| $I_{LI}$                         | Input Leak Current (T1, INT)                             | $v_{SS} \leq v_{IN} \leq v_{CC}$                       | -    | -    | ±10             | μА   |

| $I_{LI1}$                        | Input Leak Current (P10-17, P20-P27, EA, SS)             | V <sub>SS</sub> +0.45≦V <sub>IN</sub> ≦V <sub>CC</sub> | -    | -    | -500            | μA   |

| $I_{ m LO}$                      | Output Leak Current (BUS, TO) (High impedance condition) | v <sub>SS</sub> +0.45≦v <sub>IN</sub> ≤v <sub>CC</sub> | -    | _    | ±10             | μA   |

| $I_{DD}$                         | V <sub>DD</sub> Supply Current                           |                                                        | -    | -    | 50              | mA   |

| I <sub>DD</sub> +I <sub>CC</sub> | Total Supply Current                                     |                                                        | -    | -    | 170             | mA   |

MCU48-59

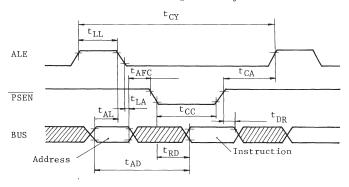

#### AC CHARACTERISTICS

TA=0°C to 70°C,  $V_{CC}=V_{DD}=+5V\pm10\%$ ,  $V_{SS}=0V$ , Unless Otherwise Noted.

|                 | IA-0 0 to 70 t                     | C, ACC=ADD=+2ATIO%               | vss-ov, | onicas        | Other                     | WISE NO | rteu. |

|-----------------|------------------------------------|----------------------------------|---------|---------------|---------------------------|---------|-------|

| SYMBOL          | PARAMETER                          | TEST CONDITION                   | l       | 049P/<br>039P | TMP8049P-6/<br>TMP8039P-6 |         | UNITS |

|                 |                                    |                                  | MIN.    | MAX.          | MIN.                      | MAX.    |       |

| $t_{ m LL}$     | ALE Pulse Width                    |                                  | 150     | -             | 400                       | _       | ns    |

| t <sub>AL</sub> | Address Setup Time (ALE)           |                                  | 70      | -             | 150                       | -       | ns    |

| t <sub>LA</sub> | Address Hold Time (ALE)            |                                  | 50      | -             | 80                        | -       | ns    |

| tcc             | Control Pulse Width (PSEN, RD, WR) |                                  | 300     | -             | 700                       | _       | ns    |

| t <sub>DW</sub> | Data Setup Time (WR)               |                                  | 250     | -             | 500                       | -       | ns    |

| t <sub>WD</sub> | Data Hold Time (WR)                | $C_{L=20pF}$                     | 40      | -             | 120                       | -       | ns    |

| t <sub>CY</sub> | Cycle Time                         | 11MHz XTAL<br>(6MHz XTAL for -6) | 1.36    | 15.0          | 2.5                       | 15.0    | μs    |

| t <sub>DR</sub> | Data Hold Time (PSEN, RD)          |                                  | 0       | 100           | 0                         | 200     | ns    |

| t <sub>RD</sub> | Data Input Read Time<br>(PSEN, RD) |                                  | _       | 200           | -                         | 500     | ns    |

| t <sub>AW</sub> | Address Setup Time (WR)            |                                  | 200     | -             | 230                       | _       | ns    |

| t <sub>AD</sub> | Address Setup Time<br>(Data Input) |                                  | -       | 400           | _                         | 950     | ns    |

| tAFC            | Address Float Time (RD, PSEN)      |                                  | -10     | -             | 0                         | _       | ns    |

| t <sub>CP</sub> | Port Control Setup Time (PROG)     |                                  | 100     | -             | 110                       | -       | ns    |

| t <sub>PC</sub> | Port Control Hold Time (PROG)      |                                  | 60      | -             | 130                       | _       | ns    |

| t <sub>PR</sub> | Port 2 Input Data Set Time (PROG)  |                                  | _       | 650           | _                         | 810     | ns    |

| t <sub>DP</sub> | Output Data Setup Time<br>(PROG)   |                                  | 200     | -             | 220                       | _       | ns    |

| t <sub>PD</sub> | Output Data Hold Time<br>(PROG)    |                                  | 20      | _             | 65                        | -       | ns    |

| t <sub>PF</sub> | Port 2 Input Data Hold Time (PROG) |                                  | 0       | 150           | 0                         | 150     | ns    |

| tpp             | PROG Pulse Width                   |                                  | 700     | -             | 1510                      | -       | ns    |

| t <sub>PL</sub> | Port 2 I/O Data Setup Time         |                                  | 250     | -             | 500                       | -       | ns    |

| t <sub>LP</sub> | Port 2 I/O Data Hold Time          |                                  | 120     | _             | 150                       | _       | ns    |

|                 |                                    |                                  |         |               |                           |         |       |

Control Outputs :  $C_L$ =80pF, BUS Outputs :  $C_L$ =150pF

#### TMP8049PI-6/8039PI-6: INDUSTRIAL SPECIFICATION.

#### ABSOLUTE MAXIMUM RATINGS

| SYMBOT,           | ITEM                                                                    | RATING         |

|-------------------|-------------------------------------------------------------------------|----------------|

| $v_{\mathrm{DD}}$ | V <sub>DD</sub> Supply Voltage (with respect to GND (V <sub>SS</sub> )) | -0.5V to +7V   |

| $v_{cc}$          | $ m ^{VCC}$ Supply Voltage (with respect ro GND (V $_{ m SS}$ ))        | -0.5V to +7V   |

| VINA              | Input Voltage (Except EA)                                               | -0.5V to +7V   |

| $v_{INB}$         | Input Voltage (Only EA)                                                 | -0.5V to +13V  |

| PD                | Power Dissipation (Ta=25°C)                                             | 1.5W           |

| TSOLDER           | Soldering Temperature (Soldering Time 10 sec.)                          | 260°C          |

| $T_{\rm STG}$     | Storage Temperature                                                     | -55°C to 150°C |

| T <sub>OPR</sub>  | Operating Temperature                                                   | -40°C to 85°C  |

DC CHARACTERISTICS TA=-40°C to 85°C ,  $v_{CC}=v_{DD}=+5v^410\%$ ,  $v_{SS}=0v$ , Unless Otherwise Noted.

|                         | 14-40 C to 83 C 1, vCC                                   | T 10%, 188                                             | O V , O |      |              |      |

|-------------------------|----------------------------------------------------------|--------------------------------------------------------|---------|------|--------------|------|

| SYMBOL                  | PARAMETER                                                | TEST CONDITIONS                                        | MIN.    | TYP. | MAX.         | UNIT |

| $\Lambda^{\mathrm{LT}}$ | Input Low Voltage                                        |                                                        | -0.5    | -    | 0.6          | V    |

| Λ <sup>I H</sup>        | Input High Voltage (Except XTAL1, XTAL2, RESET)          |                                                        | 2.2     | _    | $v_{\rm CC}$ | V    |

| $v_{TH1}$               | Input High Voltage<br>(XTAL1, XTAL2, RESET)              |                                                        | 3.8     | _    | $v_{\rm CC}$ | V    |

| $v_{\mathrm{OL}}$       | Output Low Voltage (BUS)                                 | IOL=1.6mA                                              | _       | _    | 0.45         | V    |

| v <sub>OL1</sub>        | Output Low Voltage (RD, WR, PSEN, ALE)                   | I <sub>OL</sub> =1.6mA                                 | -       | • _  | 0.45         | V    |

| $v_{\rm OL2}$           | Output Low Voltage (PROG)                                | 1 <sub>01</sub> =0.8mA                                 | -       |      | 0.45         | V    |

| V <sub>O1</sub> ,3      | Output Low Voltage<br>(For other output pins)            | I <sub>OL=1.2mA</sub>                                  | _       | _    | 0.45         | V    |

| $v_{\mathrm{OH}}$       | Output High Voltage (BUS)                                | I <sub>OH</sub> =-80µA                                 | 2.4     | _    | -            | V    |

| $v_{\mathrm{OH1}}$      | Output High Voltage (RD, WR, PSEN, ALE)                  | I <sub>OH</sub> =-80µA                                 | 2.4     | _    | -            | V    |

| v <sub>OH2</sub>        | Output High Voltage<br>(For other output pins)           | I <sub>OH</sub> =- 30 <sub>μ</sub> A                   | 2.4     | _    | _            | v    |

| $I_{LI}$                | Input Leak Current (T1, INT)                             | VSS=VIN=VCC                                            | _       | -    | ±10          | μА   |

| $I_{LI1}$               | Input Leak Current (P10-17, P20-P27, EA, SS)             | V <sub>SS</sub> +0.45≦V <sub>IN</sub> ≤V <sub>CC</sub> | _       | -    | -700         | μА   |

| $I_{LO}$                | Output Leak Current (BUS, TO) (High impedance condition) | v <sub>SS</sub> +0.45≦v <sub>IN</sub> ≦v <sub>CC</sub> | _       | _    | ±10          | μА   |

| $I_{DD}$                | V <sub>DD</sub> Supply Current                           |                                                        | -       | _    | 50           | mA   |

| IDD+ICC                 | Total Supply Current                                     |                                                        | -       | -    | 170          | mA   |

|        |    | <br> |  |

|--------|----|------|--|

| MCU48- | 61 |      |  |

### AC CHARACTERISTICS

TA=-40°C to 85°C, VCC=VDD=+5V±10%, VSS=0V, Unless otherwise Noted.

|                  | TA-40 C to 65 C, VCC-VDD-+5V-10%, VSS-0V, Unitess otherwise Moteut. |                 |      |      |      |      |  |  |  |  |

|------------------|---------------------------------------------------------------------|-----------------|------|------|------|------|--|--|--|--|

| SYMBOL           | PARAMETER                                                           | TEST CONDITIONS | MIN. | TYP. | MAX. | UNIT |  |  |  |  |

| $t_{ m LL}$      | ALE Pulse Width                                                     |                 | 200  | _    | -    | ns   |  |  |  |  |

| t <sub>AL</sub>  | Address Setup Time (ALE)                                            |                 | 120  | _    | _    | ns   |  |  |  |  |

| t <sub>LA</sub>  | Address Hold Time (ALE)                                             |                 | 80   | -    | _    | ns   |  |  |  |  |

| t <sub>CC</sub>  | Control Pulse Width(PSEN, RD, WR)                                   |                 | 400  | _    | _    | ns   |  |  |  |  |

| t <sub>DW</sub>  | Data Setup Time (WR)                                                |                 | 420  | _    | _    | ns   |  |  |  |  |

| t <sub>WD</sub>  | Data Hold Time (WR)                                                 | $C_{L=20pF}$    | 80   | -    | -    | ns   |  |  |  |  |

| t <sub>CY</sub>  | Cycle Time                                                          |                 | 2.5  | -    | 15.0 | μs   |  |  |  |  |

| t <sub>DR</sub>  | Data Hold Time (PSEN, RD)                                           |                 | 0    | -    | 200  | ns   |  |  |  |  |

| t <sub>RD</sub>  | Data Input Read Time (PSEN, RD)                                     |                 | -    | _    | 400  | ns   |  |  |  |  |

| t <sub>AW</sub>  | Address Setup Time (WR)                                             |                 | 230  | -    | _    | ns   |  |  |  |  |

| t <sub>AD</sub>  | Address Setup Time (Data Input)                                     |                 | -    | _    | 600  | ns   |  |  |  |  |

| t <sub>AFC</sub> | Address Float Time (RD, PSEN)                                       |                 | -40  | -    | -    | ns   |  |  |  |  |

| t <sub>CA</sub>  | Internal between Control Pulse and ALE                              |                 | 10   | _    | -    | ns   |  |  |  |  |

| t CP             | Port Control Setup Time(PROG)                                       |                 | 115  | -    | -    | ns   |  |  |  |  |

| t <sub>PC</sub>  | Port Control Hold Time (PROG)                                       |                 | 65   | _    | _    | ns   |  |  |  |  |

| t <sub>PR</sub>  | Port 2 Input Data Set Time(PROG)                                    |                 | -    | _    | 860  | ns   |  |  |  |  |

| t <sub>DP</sub>  | Output Data Setup Time(PROG)                                        |                 | 230  | _    | -    | ns   |  |  |  |  |

| t <sub>PD</sub>  | Output Data Hold Time (PROG)                                        |                 | 25   | -    | -    | ns   |  |  |  |  |

| t <sub>PF</sub>  | Port2 Input Data Hold Time(PROG)                                    |                 | 0    | -    | 160  | ns   |  |  |  |  |

| t <sub>PP</sub>  | PROG Pulse Width                                                    |                 | 920  | -    | -    | ns   |  |  |  |  |

| t <sub>PL</sub>  | Port 2 I/O Data Setup Time                                          |                 | 300  | -    | -    | ns   |  |  |  |  |

| t <sub>LP</sub>  | Port 2 I/O Data Hold Time                                           |                 | 120  | _    | -    | ns   |  |  |  |  |

Note : tcy=2.5  $\mu s$  , Control Output:  $C_L = 80 pF$  , BUS Output:  $C_L = 150 pF$  , PORT 20-23:  $C_L = 80 pF$  .

#### TIMING WAVEFORM

#### A. Instruction Fetch from External Program Memory

#### B. Read from External Data Memory

#### C. Write into External Data Memory

#### D. Timing of Port 2 during Expander Instruction Execution

#### TYPICAL CHARACTERISTICS

MCU48-64

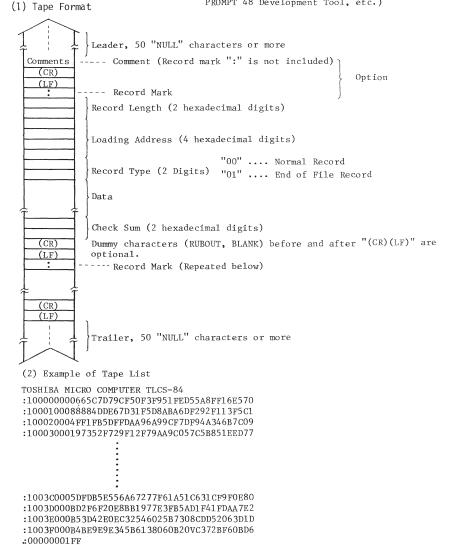

#### PROGRAM TAPE FORMAT

TMP8049 programs are delivered in the form of paper tape with the following format and it is required to attach the tape list. The format of paper tape is same as the Intel type object tape (hexadecimal tape output by Intel MDS system,

(1) Tape Format

PROMPT 48 Development Tool, etc.)

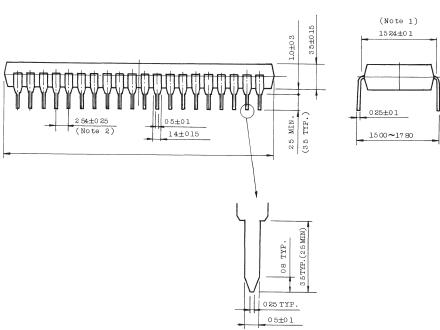

Note: 1. This dimension is measured at the center of bending point of leads.

2. Each lead pitch is 2.54mm, and all the leads are located within  $\pm 0.25mm$  from their theoritical positions with respect to No.1 and No.40 leads.